## IEEE Standard Test Specifications for Avalanche Junction Semiconductor Surge Protective Devices

Sponsor

Surge Protective Devices Committee of the IEEE Power Engineering Society

Approved September 10, 1987

**IEEE Standards Board**

Copyright © 1989 by

The Institute of Electrical and Electronics Engineers, Inc 345 East 47th Street, New York, NY 10017, USA

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

**IEEE Standards** documents are developed within the Technical Committees of the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside of IEEE which have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old, and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason IEEE and the members of its technical committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board 345 East 47th Street New York, NY 10017 USA

IEEE Standards documents are adopted by the Institute of Electrical and Electronics Engineers without regard to whether their adoption may involve patents on articles, materials, or processes. Such adoption does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the standards documents.

#### **Foreword**

(This Foreword is not a part of IEEE C62.35-1987, IEEE Standard Test Specifications for Avalanche Junction Semiconductor Surge-Protective Devices.)

This test specification has been developed for the purpose of testing and evaluating avalanche junction semiconductor type surge protective devices.

These devices are used as a surge diverter for limiting transient overvoltages in power and communications circuits. These devices are similar to a standard Zener diode except that they provide a sharper avalanche characteristic than the Zener and they are designed for short time-frame occurrences than continuous regulation.

The interest in low-voltage avalanche junction semiconductor surge protective devices has grown with the trend to highly sophisticated electrical and electronic devices which are exposed to surges from the environment. Initially, there were a few standard terms or tests to define or compare these devices. The IEEE Surge Protection Devices Committee formed its Low Voltage Surge Protection Devices Working Group in 1970 to define these parameters.

Experts were drawn from many fields in communications and power utilities, electronic manufacturers and users, test equipment manufacturers and laboratories, and producers of avalanche junction semiconductor surge protective devices. The requirements, experiences, and vocabularies of these representatives were melded to produce this document as a guide to potential users of these devices.

At the time this document was approved by the Low-Voltage Surge Protection Devices Committee of the Power Engineering Society of the IEEE, members on the Low-Voltage Solid-State Surge Protective Devices Working Group 3.6.2 had the following membership who contributed to the writing of this document:

## R. Odenberg, Chair

| L. Baker       | J. Kawiecki     | L. D. Sweeney |

|----------------|-----------------|---------------|

| B. Braskich    | F. D. Martzloff | L. Williams   |

| T. F. Hock     | P. Richman      | P. Winch      |

| D. W. Hutchins | P. D. Speranza  | G. Zappe      |

The following persons were on the balloting committee that approved this document for submission to the IEEE Standards Board:

| C. D. Hansell    | J. J. Napiorkowski                                                                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | R. Odenberg                                                                                                                                                                |

| D. E. Hedman     | W. R. Ossman                                                                                                                                                               |

| J. A. Hetrick    | J. C. Osterhout                                                                                                                                                            |

| A. R. Hileman    | M. Parente                                                                                                                                                                 |

| W. W. Hines      | S. A. Potocny                                                                                                                                                              |

| D. W. Jackson    | P. Richman                                                                                                                                                                 |

| I. B. Johnson    | P. D. Speranza                                                                                                                                                             |

| S. S. Kershaw    | K. B. Stump                                                                                                                                                                |

| J. L. Koepfinger | A. Sweetana                                                                                                                                                                |

| J. A. Mambuca    | E. R. Taylor                                                                                                                                                               |

| E. H. Marrow     | A. C. Westrom                                                                                                                                                              |

| F. D. Martzloff  | S. G. Whisenant                                                                                                                                                            |

| D. J. Melvold    | E. J. Yasuda                                                                                                                                                               |

|                  | G. S. Haralampu D. E. Hedman J. A. Hetrick A. R. Hileman W. W. Hines D. W. Jackson I. B. Johnson S. S. Kershaw J. L. Koepfinger J. A. Mambuca E. H. Marrow F. D. Martzloff |

Other individuals who contributed reviews and comments are:

M. Flack J. L. Koepfinger E. C. Sakshaug G. L. Gaibrois L. McAfee\* B. I. Wolff

#### Chairman until 1980

When the IEEE Standards Board approved this standard on September 10, 1987, it had the following membership:

Donald C. Fleckenstein, Chair Marco Migliaro, Vice Chair Andrew G. Salem, Secretary

James H. Beall Dennis Bodson Marshall L. Cain James M. Daly Stephen R. Dillon Eugene P. Fogarty Jay Forster Kenneth D. Hendrix

Irvin N. Howell

Leslie R. Kerr Jack Kinn Irving Kolodny Joseph L. Koepfinger\* Edward Lohse John May Lawrence V. McCall L. Bruce McClung Donald T. Michael\*

L. John Rankine John P. Riganati Gary S. Robinson Frank L. Rose Robert E. Rountree William R. Tackaberry William B. Wilkens Helen M. Wood

<sup>\*</sup>Member emeritus

| CLA | NUSE                                                                                                                           | PAGE |

|-----|--------------------------------------------------------------------------------------------------------------------------------|------|

| 1.  | Scope                                                                                                                          | 1    |

|     | 1.1                                                                                                                            | 1    |

|     | 1.2                                                                                                                            | 1    |

|     | 1.3                                                                                                                            | 1    |

|     | 1.4                                                                                                                            | 2    |

| 2.  | Definitions of Rated and Other Parameters                                                                                      | 2    |

|     | 2.1 Rated Parameter Values                                                                                                     |      |

|     | 2.2 Definitions                                                                                                                |      |

|     | 2.3 Additional Descriptions                                                                                                    | 3    |

| 3.  | Service Conditions                                                                                                             | 9    |

|     | 3.1 Normal Service Conditions                                                                                                  |      |

|     | 3.2 Unusual Service Conditions                                                                                                 | 9    |

| 4.  | Standard Design Test Procedure                                                                                                 | 10   |

|     | 4.1 Standard Design Test Criteria                                                                                              |      |

|     | 4.2 Statistical Procedures                                                                                                     |      |

|     | 4.3 Test Conditions                                                                                                            |      |

|     | 4.4 Clamping Voltage Test (V <sub>C</sub> ) (see Fig 2)                                                                        |      |

|     | 4.5 Rated Multiple Peak Impulse Current (I <sub>PP</sub> ) (see Fig 2)                                                         | 11   |

|     | 4.6 Rated Stand-off Voltage (V <sub>WM</sub> ) (see Fig 3), and Rated Working RMS Voltage [V <sub>WM(RMS)</sub> ] (see Fig 3). | 11   |

|     | 4.7 Maximum Stand-By Current (I <sub>D</sub> ) (see Fig 3).                                                                    |      |

|     | 4.8 Rated Peak Single Surge Transient Current (I <sub>SM</sub> ) (see Fig 2)                                                   |      |

|     | 4.9 Lifetime Rated Pulse Current Tests (see Fig 2)                                                                             |      |

| 5.  | Failure Modes                                                                                                                  | 12   |

|     | 5.1 Degradation Failure Mode                                                                                                   | 12   |

|     | 5.2 Short Circuit Failure Mode                                                                                                 |      |

|     | 5.3 Open Circuit Failure Mode                                                                                                  |      |

|     | 5.4 High Clamping Voltage Failure Mode                                                                                         |      |

|     | 5.5 "Fail-Safe" Operation                                                                                                      |      |

| 6.  | Derived Parameters and Other Test Procedures                                                                                   | 13   |

|     | 6.1 Breakdown Voltage (Avalanche) Test [V <sub>(BR)</sub> ] (see Fig 4.)                                                       |      |

|     | 6.2 Rated Multiple Peak Pulse Power Dissipation (P <sub>PPM</sub> ).                                                           |      |

|     | 6.3 Rated Average Power Dissipation [P <sub>M(AV)</sub> ]                                                                      |      |

|     | 6.4 Capacitance Test (C)                                                                                                       |      |

|     | 6.5 Peak Overshoot Voltage (V <sub>OS</sub> ) (See Fig 5).                                                                     |      |

|     | 6.6 Response Time Overshoot Duration (see Fig 5)                                                                               |      |

|     | 6.7 Rated Forward Surge Current (I <sub>FSM</sub> ) (see Fig 3)                                                                |      |

|     | 6.8 Forward Voltage (V <sub>FS</sub> ).                                                                                        |      |

|     | 6.9 Temperature Derating (see Fig 6)                                                                                           |      |

|     | 6.10 Thermal Resistance ( $R_{\theta JA}$ or $R_{\theta JC}$ or $R_{\theta JL}$ )                                              |      |

|     | 6.11 Temperature Coefficient of Breakdown Voltage [°CV(BR)]                                                                    | 16   |

| 7.  | Bibliography                                                                                                                   | 16   |

# IEEE Standard Test Specifications for Avalanche Junction Semiconductor Surge Protective Devices

## 1. Scope

#### 1.1

This standard applies to a two terminal avalanche junction surge suppressor for surge protective application on systems with dc to 420 Hz frequency and voltages equal to or less than 1000 V rms or 1200 V dc. The avalanche junction surge suppressor is a semiconductor diode which can operate in either the forward or reverse direction of its V-I characteristic. The device is a single package which may be assembled from any combination of series and/or parallel diode chips. This standard contains definitions, service conditions, and a series of test criteria for determining the electrical characteristics of these semiconductor avalanche junction surge suppressors. If the characteristics differ with the direction of conduction, then each direction of conduction shall be separately specified. Arresters are covered in ANSI/IEEE C62.1-1984 [1] <sup>2,3</sup> and ANSI/IEEE C62.33-1982 [2].

#### 1.2

The tests in this standard are intended as design tests as defined in ANSI/IEEE Std 100-1988 [4] and provide a means of comparison among various avalanche junction surge-protective devices.

#### 1.3

Semiconductor avalanche junction surge suppressors are a class of diodes that are designed to conduct the surge currents necessary to provide transient overvoltage protection in electrical circuits. Other types of diodes may exhibit surge capability. Unless their surge characteristics have been defined according to this specification, they should not be used as surge suppressors. Avalanche junction surge suppressors exhibit a relatively high impedance at normal system voltages before and after the surge. They limit surge voltages on equipment by providing a low impedance to conduct

<sup>&</sup>lt;sup>1</sup>Diodes used in the forward direction only for the purpose of surge protection may also be tested in accordance with these specifications.

<sup>&</sup>lt;sup>2</sup>The numbers in brackets correspond to the standards listed in the Bibliography, Section 7 of this standard.

<sup>&</sup>lt;sup>3</sup>ANSI/IEEE publications can be obtained from the Sales Department, American National Standards Institute, 1430 Broadway, New York, NY 10018, or from the Institute of Electrical and Electronics Engineers, Service Center, Piscataway, NJ 08854.

the surge discharge current. More specifically, this standard applies to such devices having a monotonic increase in voltage with increasing current flow.

Test criteria and definitions in this standard provide a common engineering language beneficial to user and manufacturer of surge-protective devices.

## 1.4

Due to the voltage and energy levels employed in the majority of tests described herein, all tests should be considered hazardous and appropriate caution should be taken in their performance.

## 2. Definitions of Rated and Other Parameters

#### 2.1 Rated Parameter Values

For the purpose of this standard, the values of rated parameters are established by the manufacturer, according to statistical acceptance criteria as indicated in 4.2.

#### 2.2 Definitions

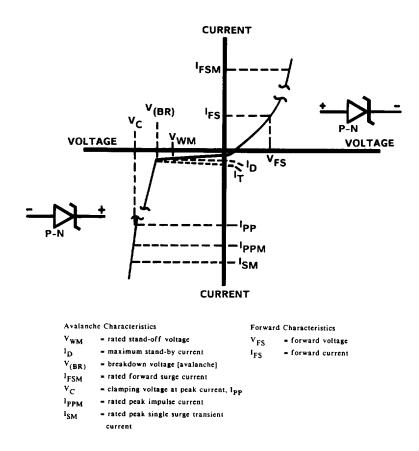

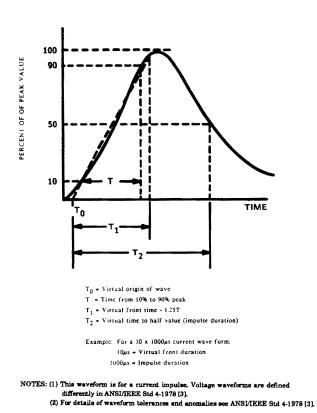

Definitions in this section apply to devices having symmetrical volt-ampere characteristics or asymmetrical volt-ampere characteristics. The specified tests are to be performed at a nominal 25 °C ambient temperature unless otherwise indicated. If the voltampere characteristics are asymmetrical, then the characteristic values shall be specified for each polarity. The relation between some common terms on a typical V-I graph is illustrated in Fig 1. For the method of defining impulse waveforms, see ANSI/IEEE Std 4-1978 [3], and Fig 7 of this standard. The terms defined by 2.2.1-2.2.7 are the minimum necessary to characterize the device.

| Term and Description                                                                                                                                                                                                                                                                                                       | Symbol            | Reference                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------|

| <b>2.2.1 Clamping Voltage.</b> Peak voltage across the semiconductor avalanche surge suppressor measured at I <sub>PP</sub> . (Note: I <sub>PP</sub> is a peak impulse current at a specified waveform. Due to thermal, reactive, or other effects, peak voltage and peak current are not necessarily coincident in time.) | $V_{\mathrm{C}}$  | See 4.4 and Figs 1 and 2     |

| <b>2.2.2 Rated Peak Impulse Current.</b> Rated maximum value of peak impulse current ( $I_{PP}$ ) applied for 10 pulses with $10 \times 1000~\mu s$ waveform and maximum duty factor of 0.01% without causing failure.                                                                                                     | ${ m I}_{ m PPM}$ | See 4.5 and Figs 1, 2, and 6 |

| <b>2.2.3 Rated Stand-Off Voltage.</b> Maximum working (continuous) dc or peak voltage that may be applied over the standard operating service temperature range.                                                                                                                                                           | $V_{ m WM}$       | See 4.6 and Figs 1 and 3     |

| <b>2.2.4 Stand-By Current.</b> Maximum current that flows through a surge suppressor junction at rated stand-off voltage $(V_{WM})$ for a specified temperature.                                                                                                                                                           | $I_D$             | See 4.7 and Figs 1 and 3     |

| <b>2.2.5 Rated Working RMS Voltage.</b> Maximum continuous sinusoidal rms voltage which may be applied over the standard operating service temperature range.                                                                                                                                                              | $V_{MW(RMS)}$     | See 4.6 and Fig 3            |

| 2.2.6 Rated Peak Single Surge Transient Current. Maximum value of peak impulse current ( $I_{PP}$ ) which may be applied for a single $10 \times 1000 \ \mu s$ impulse without causing device failure. Maximum clamping voltage ( $V_C$ ) is obtained when measured at $I_{SM}$ .                                          | $I_{SM}$          | See 4.8 and Figs 1 and 2     |

| <b>2.2.7 Lifetime Rated Pulse Currents.</b> Rated values of the peak impulse current $(I_{PP})$ as a function of the number of pulses and wave-shape, which may be applied over the device rated lifetime.                                                                                                                 |                   | See 4.9 and Fig 2            |

| <b>2.3 Additional Descriptions.</b> For certain applications some of the terms covered in 2.3.1 through 2.3.15 may be useful.                                                                                                                                                                                              |                   |                              |

| <b>2.3.1 Breakdown Voltage (Avalanche).</b> The voltage measured across the avalanche junction surge suppressor at a specified pulse dc current on the V-I curve at which avalanche occurs.                                                                                                                                | $V(_{BR})$        | See 6.1 and Figs 1 and 4     |

| Term and Description                                                                                                                                                                                                                                                                                                                     | Symbol                 | Reference                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------|

| <b>2.3.2 Rated Multiple Peak Pulse Power Dissipation.</b> Peak pulse power dissipation resulting from the pulse current, $I_{PP}$ . $P_{PPM} = V_C \times I_{PPM}$ .                                                                                                                                                                     | $P_{\mathrm{PPM}}$     | By calculation, see 6.2 and Fig 6  |

| <b>2.3.3 Rated Average Power Dissipation.</b> Maximum average power dissipation in the device due to repetitive pulses at a specified current and temperature without causing device failure.                                                                                                                                            | $P_{M(AV)}$            | By evaluation, see 6.3             |

| <b>2.3.4 Clamping Factor.</b> Ratio of the measured clamping voltage $(V_C)$ at a specified peak pulse current $I_{PP}$ to breakdown voltage.                                                                                                                                                                                            | CF                     | By computation shown               |

| $CF = \frac{V_C}{V_{(BR)}}$                                                                                                                                                                                                                                                                                                              |                        |                                    |

| <b>2.3.5 Voltage Clamping Ratio.</b> A figure of merit, which determines the clamping effectiveness of an avalanche surge suppressor as defined by the symbols.                                                                                                                                                                          | $\frac{V_{C}}{V_{WM}}$ | By computation shown               |

| <b>2.3.6 Incremental Surge Resistance.</b> Resistance composed of thermal and nonlinear avalanche characteristics calculated between two instantaneous sets of values for peak pulse current ( $I_{PP}$ ) and clamping voltage ( $V_C$ ) with a specified waveform. $R_S = \frac{V_{C_2} - V_{C_1}}{I_{PP_2} - I_{PP_1}}$                | $R_{\mathrm{S}}$       | See 4.4 and by computation shown   |

| <b>2.3.7 Capacitance.</b> Capacitance between the two terminals of an avalanche surge suppressor measured at specific frequency and bias.                                                                                                                                                                                                | С                      | See 6.4                            |

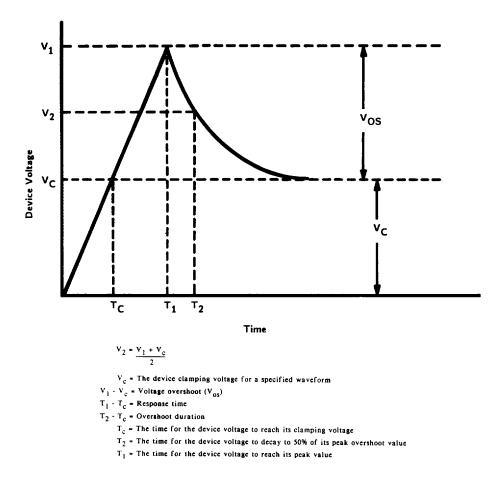

| <b>2.3.8 Voltage Overshoot.</b> The excess voltage above the clamping voltage ( $V_C$ ) of the device for a given current that occurs when current waves of less than 10 $\mu$ s virtual front duration are applied. This value may be expressed as a percentage of the clamping voltage ( $V_C$ ) for a 10 x 1000 $\mu$ s current wave. | V <sub>OS</sub>        | See 6.5 and Fig 5                  |

| <b>2.3.9 Response Time.</b> The time between the point at which the wave exceeds the clamping level $(V_{\rm C})$ and the peak of the voltage overshoot.                                                                                                                                                                                 |                        | Definition only, see 6.6 and Fig 5 |

| <b>2.3.10 Overshoot Duration.</b> The time between the point at which the wave exceeds the clamping voltage level $V_{\rm C}$ and the point at which the voltage overshoot has decayed to 50% of its peak.                                                                                                                               |                        | Definition only, see 6.6 and Fig 5 |

| <b>2.3.11 Rated Forward Surge Current.</b> Maximum single peak current for an 8.3 ms, half sine wave, without causing device failure. Applies to asymmetrical bidirectional avalanche junction surge suppressors only.                                                                                                                   | $I_{\mathrm{FSM}}$     | See 6.7 and Figs 1 and 3           |

| Term and Description                                                                                                                                                                                                                                                  | Symbol                                                   | Reference                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|

| <b>2.3.12 Forward Voltage.</b> Peak voltage measured across the avalanche surge suppressor for a specified forward pulse current $I_{FS}$ . Applies to asymmetrical bidirectional avalanche junction surge suppressors only.                                          | $ m V_{FS}$                                              | See 6.8 and Fig 1                  |

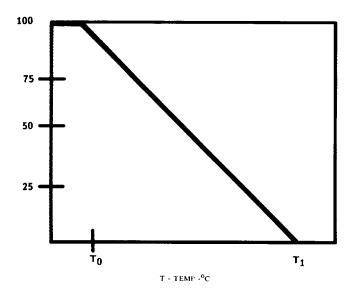

| <b>2.3.13 Temperature Derating.</b> Derating with temperature above a specified base temperature, expressed as a percentage, such as may be applied to peak pulse power and peak pulse current.                                                                       |                                                          | Definition only, see 6.9 and Fig 6 |

| <b>2.3.14 Thermal Resistance.</b> Junction to ambient, case, or lead temperature rise per unit input of applied power expressed as degree Celcius per Watt.                                                                                                           | R <sub>θJA</sub><br>R <sub>θJC</sub><br>R <sub>θJL</sub> | Definition only, see 6.10          |

| <b>2.3.15 Temperature Coefficient of Breakdown Voltage.</b> The ratio of the change in breakdown voltage $[V_{(BR)}]$ to changes in temperature. Expressed as either millivolts per degree Celsius or percent per degree Celsius $(mV)^{\circ}C$ or $\%/^{\circ}C$ ). | °°V <sub>(BR)</sub>                                      | See 6.11                           |

Figure 1—V-I Graph Illustrating Symbols and Terms for P-N Avalanche Junction

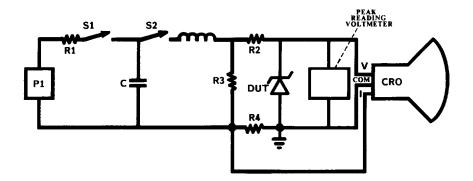

- P1 = Charging network or supply

- R1 Charging resistor

- S1 = Charging switch

- S2 Impulse discharge switch

- L Impulse shaping inductor

- R2 Impulse shaping and current limiting resistor

- C = Impulse shaping capacitor and generator

- R3 = Impulse shaping resistor

- R4 = Current sensing resistor (coaxial)\*

- DUT Device under test

- CRO = Oscilloscope for observing current and/or voltage

CAUTION: The circuit shown is for description only. Measurement techniques for high current, high frequency testing should be observed, such as, four point probe Kelvin contacts, differential oscilloscope, preamplifier, short leads, etc.

Alternately use a pulse rated current transformer specified for the peak current and duration involved.

Figure 2—Test Circuit for Clamping Voltage ( $V_C$ ), Peak Impulse Current ( $I_{PPM}$ ,  $I_{PP}$ ), and Rated Peak Single Surge Transient Current ( $I_{SM}$ )

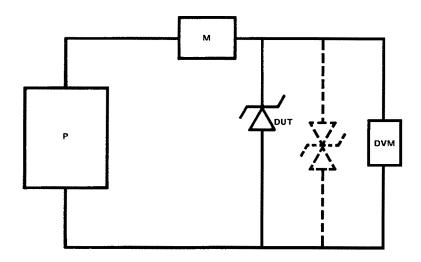

- P = Adjustable DC voltage power supply (AC supply if AC test)

- M = Microammeter DC (AC ammeter if AC test)

- DUT = Device under test

DVM = Digital voltmeter (substitute oscilloscope if AC test)

Figure 3—Test Current for Verifying Stand-Off Voltage, Stand-By Current, and Rated Working RMS Voltage  $(V_{WM})$ ,  $(I_D)$ ,  $[V_{WM(RMS)}]$

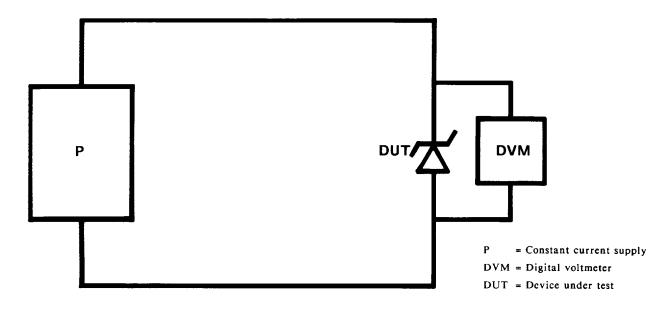

Figure 4—Test Circuit for Verifying Breakdown Voltage (V<sub>(BR)</sub>

Figure 5—Graph Illustrating Voltage Overshoot, Response Time, and Overshoot Duration

#### JUNCTION SEMICONDUCTOR SURGE-PROTECTIVE DEVICES

Rated Peak Multiple Pulse Power ( $P_{PPM}$ ) or Current ( $I_{PPM}$ ,  $I_{SM}$ ) in Percent of  $T_0$   $^{o}C$  Rating

T<sub>0</sub> = Temperature at which derating begins

T<sub>1</sub> = Temperature at which there is no power or current allowed

Figure 6—Derating Curve for Avalanche Junction Surge Suppressor

Figure 7—Impulse Current Waveform

#### 3. Service Conditions

#### 3.1 Normal Service Conditions

In the absence of special requirements the following items should be specified by the manufacturer as appropriate.

#### 3.1.1 Environmental Conditions

- 1) Operating and storage temperature ranges

- 2) Humidity

- 3) Mechanical shock and vibration

## 3.1.2 Physical Properties

- 1) Solvent resistance

- 2) Solderability

- 3) Flammability

- 4) Package rupture during overload

- 5) Electrical connection to metal case

## 3.1.3 System Conditions

- 1) Nominal systems frequencies

- 2) Maximum continuous system voltage

- 3) Peak impulse currents

- 4) Transient repetition rate.

#### 3.1.4 Surge Rating of the avalanche Junction Suppressor under System Conditions

- 1) Rated average power dissipation  $P_{M(Av)}$

- 2) Peak pulse power or current temperature derating

- 3) Lifetime rated pulse currents.

## 3.2 Unusual Service Conditions

The following service conditions may require special consideration in the design or application of avalanche junction suppressors and should be called to the attention of the manufacturer.

## 3.2.1 Environmental Conditions

- 1) Ambient temperature exceeding the normal service conditions

- 2) Exposure to:

- a) Damaging fumes or vapors

- b) Excessive dirt or current conducting deposits, excessive humidity, moisture, dripping water, steam or salt spray, explosive atmosphere, abnormal vibrations and shocks

- 3) Unusual transportation or storage conditions

- 4) Significance of flammability.

## 3.2.2 Physical Conditions

Limitation on weight or space, including clearance to nearby conducting objects.

#### 3.2.3 System Conditions

- 1) System voltages, current repetition rate or frequency operating conditions whereby the ratings of the devices are exceeded (see Sec 5, Failure Modes)

- 2) System impulse currents not within the rating of the device (see Sec 5, Failure Modes)

- 3) Exposure to direct lightning strike (see Sec 5, Failure Modes)

- 4) Electromagnetic field effects (see Sec 5, Failure Modes)

- 5) Unusual ground potential situations (see Sec 5, Failure Modes)

- 6) Any other unusual conditions known to the user.

## 4. Standard Design Test Procedure

#### 4.1 Standard Design Test Criteria

The design tests described in 4.4 through 4.9 provide standardized methods for measuring specified parameters of an avalanche junction suppressor. These parameters may vary from device to device making it necessary to provide statistical descriptions of the device characteristics in order to compare products.

#### 4.2 Statistical Procedures

The following procedure shall be used to describe any characteristics that have been determined to have important statistical aspects. A product sample shall be chosen in a manner consistent with the definition of design tests as provided by ANSI/IEEE Std 100-1988 [4]. A sufficient number of devices shall be tested and the characteristics in question measured or ratings verified as described in the applicable design test until the parameters of the underlying statistical distribution are determined within confidence limits specified by the manufacturer. Values relating to the product sample such as, but not limited to, mean, maximum, and standard deviation may then be stated.

#### 4.3 Test Conditions

The tests of 4.4 through 4.9 should be performed on the device as required by the application. Unless otherwise specified, ambient test conditions should be as follows:

Temperature:  $25 \pm 5$  °C

Relative Humidity: Less than 85%

## 4.4 Clamping Voltage Test (V<sub>C</sub>) (see Fig 2).

#### 4.4.1

The purpose of this test is to determine the voltage protection level provided by the avalanche junction suppressor when conducting a current impulse at a specified waveform and crest value ( $I_{pp}$ ). The device shall be tested in both polarities unless otherwise specified.

#### 4.4.2

To verify the volt-ampere characteristic curve, the clamping voltage shall be measured at two current levels. The peak voltage and peak current are not necessarily coincident in time. In the absence of specific requirements, test current shall be  $0.2~I_{PP}$  and  $I_{PP}$  using a  $10\times1000~\mu s$  waveform.

## 4.5 Rated Multiple Peak Impulse Current (IPP) (see Fig 2).

The purpose of this test is to verify that an avalanche junction surge suppressor design meets a statistically expressed level of reliability when subjected to surges at its rated capability. The multiple peak impulse current rating shall be verified by subjecting the device to  $10 \times 1000 \,\mu s$  current impulses,  $I_{PP}$ . The impulse currents shall be applied for 10 pulses at a maximum rate of one pulse every 10 seconds. For symmetrical devices, a single polarity shall be tested for the 10 consecutive pulses. The failure criteria of Section 5 shall apply.

## 4.6 Rated Stand-off Voltage ( $V_{WM}$ ) (see Fig 3), and Rated Working RMS Voltage [ $V_{WM(RMS)}$ ] (see Fig 3).

The purpose of this test is to verify the maximum voltage that may be applied across an avalanche junction surge suppressor over a specified temperature range while maintaining a high impedance. In the absence of a specified condition, it is recommended that the current flow be less than I mA. This condition may vary with the user's application or circuit conditions. The rated working rms voltage applies only to symmetrical, bidirectional avalanche junction surge suppressors.

## 4.7 Maximum Stand-By Current (ID) (see Fig 3).

The purpose of this test is to verify the leakage current level of an avalanche junction surge suppressor at temperatures specified by the manufacturer. The rated stand-off voltage  $(V_{WM})$  shall be impressed across the device. A well regulated dc power supply is necessary, the current being measured after the voltage has been applied for at least 10 ms to allow stabilization of the conduction close to the long term dc value.

## 4.8 Rated Peak Single Surge Transient Current (I<sub>SM</sub>) (see Fig 2)

#### 4.8.1

The purpose of this test is to verify that an avalanche junction surge suppressor meets a statistically expressed level of reliability when subjected to a single pulse at its rated capability. The failure criteria of Section 5 shall apply.

#### 4.8.2

The device shall be subjected to one  $10 \times 1000$  µs current impulse. For symmetrical bidirectional types, a single current impulse is applied in only one direction. For asymmetrical undirectional types, a single current impulse is applied across the avalanche junction of the surge suppressor.

#### 4.9 Lifetime Rated Pulse Current Tests (see Fig 2)

#### 4.9.1

The purpose of this test is to verify that an avalanche junction surge suppressor meets a statistically expressed level of reliability when subjected to multiple pulses and/or different waveshapes corresponding to any of the lifetime rated pulse currents specified by the manufacturer. In the absence of special requirements, tests are recommended at each of the number of pulses and waveshapes listed in Table 1. The failure criteria of Section 5 shall apply at the conclusion of each group of multiple impulse tests.

#### 4.9.2

In performing the test matrix of Table 1, new samples shall be used for each current level and waveform tested. For asymmetrical devices, separate samples should be used to verify each test. In the absence of special requirements, pulses shall be applied at 0.01% duty factor. These tests do not require applications of line voltage.

Table 1— Lifetime Rated Pulse Currents\*

| Number of Pulses | 8×20μs | 10×1000μs        |

|------------------|--------|------------------|

| 1                | †      | $I_{SM}$         |

| 2                | †      | †                |

| 10               | †      | I <sub>PPM</sub> |

| 100              | †      | †                |

| 10 000           | †      | †                |

| 1 000 000        | †      | †                |

<sup>\*</sup>Design tests are defined in ANS1/IEEE Std 100-1988 [4].

#### 5. Failure Modes

In the absence of special requirements, the following criteria are suggested. Tests for determining failure shall be performed after the device temperature has returned to  $25 \pm 5$  °C.

## 5.1 Degradation Failure Mode

In this mode, the avalanche junction surge suppressor will have a stand-by current greater than the maximum specified.

#### 5.2 Short Circuit Failure Mode

In this mode, the avalanche junction surge suppressor will permanently become shorted with a resistance of less than 1 Ohm at 0.1 V dc. (This condition may occur when the maximum clamping voltage is exceeded after being subjected to a peak impulse current above the device rating, or when a device is powered beyond its average or multiple peak pulse power dissipation.)

## 5.3 Open Circuit Failure Mode

In this mode, the avalanche junction surge suppressor appears as an open circuit that has a breakdown voltage  $V_{(BR)}$  greater than 150% of the pretest value at an applied test current ( $I_T$ ), as discussed in 6.1.1. (This condition may occur if current is sustained in the device while in the shorted condition, or by an abnormally high or short duration current pulse beyond the device capability.)

## 5.4 High Clamping Voltage Failure Mode

In this mode, the avalanche junction surge suppressor has a clamping voltage greater than 120% of the pretest clamping voltage.

<sup>†</sup>Value obtained from manufacturers' specifications.

## 5.5 "Fail-Safe" Operation

The use of "fail-safe" to describe a failure mode of a device can occur in any of the modes described above. Some users may consider that the most desirable failure mode for the device is to maintain the protective function; for example, fail in the short-circuit failure mode. However, system objectives of other users can require that a particular device should fail in a high clamping failure mode in order to achieve the desired performance of the system. Thus, failure in the short mode, while considered "fail-safe" by many users, may in fact be opposite the desired ("safe") mode of other users. Therefore, the recommended practice is to describe the failure by one of the failure modes defined in 5.1 through 5.4.

## 6. Derived Parameters and Other Test Procedures

## 6.1 Breakdown Voltage (Avalanche) Test [V(BR)] (see Fig 4.).

#### 6.1.1

The avalanche junction surge suppressor shall be tested at a specified pulse dc current and at a specified temperature. The time of applied test current ( $I_T$ ) shall be less than 400 ms.

#### 6.1.2

This electrical characteristic is indicated as a minimum or can be indicated as a voltage range for the specified test current. In the absence of a specific requirement, it is recommended that the test current  $(I_T)$  be at 1 mA to ensure a device avalanche condition and minimum change due to any thermal effects.

## 6.2 Rated Multiple Peak Pulse Power Dissipation (P<sub>PPM</sub>).

This rating is specified by the manufacturer for each product and is dependent upon device manufacturing and packaging. Determination of the parameter requires the measurement of both peak pulse current and maximum clamping voltage, which may not be coincident in time with the impulse current for any given waveform. Multiplication of the peak pulse current by the clamping voltage is defined as the peak pulse power dissipation. A sufficient number of devices shall be tested and the voltage-current characteristics measured as described in 4.4 and 4.5 to obtain a statistical distribution within the confidence limits specified by the manufacturer.

## 6.3 Rated Average Power Dissipation $[P_{M(AV)}]$ .

The rated average power dissipation of an avalanche junction surge suppressor is specified by the manufacturer in order to limit device temperatures for reliable long life, taking into consideration two parameters:

- 1) Input average current through the material (junction) by repetitive transients, usually indicated by a duty cycle

- 2) The thermal resistance of the device to the environment by leads and/or heat-sink mounting as recommended by the manufacturer.

## 6.4 Capacitance Test (C)

The capacitance shall be measured at a specified frequency and bias. In the absence of a requirement relating to a special application, a frequency of 1.0 MHz and a bias of zero V dc is recommended for this test. The signal level of 0.1 volt rms is suggested for this test.

## 6.5 Peak Overshoot Voltage (V<sub>OS</sub>) (See Fig 5).

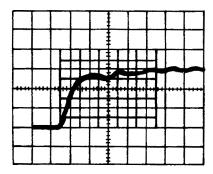

Under conditions of steep front current impulses at high amplitudes, measurement of the clamping voltage of a lead-mounted avalanche junction surge suppressor indicates values exceeding the levels observed with the standard  $10 \times 1000 \,\mu s$  waveform. This higher voltage is referred to as "overshoot". Although some small intrinsic difference can be found in the avalanche junction surge suppressor material response to steep current pulses (ac or dc), this "overshoot" is primarily attributable to the magnetic field established around the current-carrying leads of the device, which includes a voltage in the loop formed by the device leads and the protected circuit or the voltage probe used to simulate it.

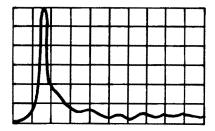

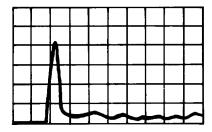

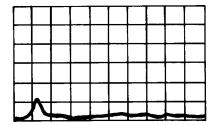

In typical applications, some lead length and loop area is unavoidable, and the associated voltage will also be impressed on the protected circuitry downstream from the avalanche junction surge suppressor. Thus, measurements of clamping voltages at steep front and high currents shall recognize the dependency of voltage "overshoot" on lead length and loop coupling rather than treat the "overshoot" as an intrinsic device characteristic. An example of "overshoot" due to lead length and loop coupling of a 30 volt suppressor is shown in Figs 8, 9, and 10. Figure 11 is the open circuit voltage waveform for this measurement.

Vertical: 2000 V/cm Horizontal: 1 ns/cm

Figure 8—Open Circuit Test Voltage Pulse Wave Front

Vertical Sensitivity: 200 V/cm Horizontal Sensitivity: 10 ns/cm

Figure 9—1.5 Inch Leads and Large Loop Area

Figure 10—0.6 Inch Leads and Medium Loop Area

Figure 11—No Leads and Small Loop Area

## 6.6 Response Time Overshoot Duration (see Fig 5)

Due to the steep wave fronts (fast rise time), response time and overshoot duration measurements require special fixtures and extremely fast responding instrumentation. Response time and overshoot duration may be a function of the waveform used for the measurement. Except for special applications, a separate test for response time and overshoot duration are not a necessary design test.

## 6.7 Rated Forward Surge Current (I<sub>FSM</sub>) (see Fig 3).

The purpose of this test is to verify that an avalanche junction surge suppressor, when subjected to an 8.3 ms, half sine wave pulse current, meets a statistical expressed level of reliability

## 6.8 Forward Voltage (V<sub>FS</sub>).

The forward voltage is measured by applying an 8.3 ms, half sine wave current (I<sub>FS</sub>) in the forward direction. Forward current is a value of current that flows through the diode in the forward direction for an asymmetrical device.

## 6.9 Temperature Derating (see Fig 6)

Temperature derating is applied to either variations in peak power or current with increasing temperatures above a specified temperature level. This is a maximum limit for an avalanche junction surge suppressor in which the power or current levels are determined at elevated temperatures.

## 6.10 Thermal Resistance ( $R_{\theta JA}$ or $R_{\theta JC}$ or $R_{\theta JL}$ ).

Thermal resistance is a measure of the flow of heat from the semiconductor junction to the case, lead, or ambient air. The thermal transfer of heat depends upon the dissipation of power to the surrounding media by means of either

radiation, natural or forced convection, or conduction through metals. The thermal characteristics of each device (family) is to be specified (and defined) by the manufacturer.

## 6.11 Temperature Coefficient of Breakdown Voltage [°cV<sub>(BR)</sub>].

The voltage temperature coefficient is the ratio of the change in breakdown voltage to the change in temperature. It may vary from device to device, but it is characteristic of a specific avalanche voltage breakdown independent of power ratings. This parameter shall be considered when operating over a temperature range. The minimum breakdown voltage and maximum clamping voltage will vary over the temperature range as a function of the voltage temperature coefficient. For breakdown voltages above 5 V, this parameter will always be positive.

## 7. Bibliography

- [1] ANSI/IEEE C62.1-1984, IEEE Standard for Surge Arresters for AC Power Circuits.

- [2] ANSI/IEEE C62.33-1982 (R1988), IEEE Standard Test Specifications for Varistor Surge-Protective Devices.

- [3] ANSI/IEEE Std 4-1978, IEEE Standard Techniques for High-Voltage Testing.

- [4] ANSI/IEEE Std 100-1988, IEEE Standard Dictionary of Electrical and Electronics Terms.